Une nouvelle puce en silicium-germanium vient d’atteindre 500 Gbps en débit sur un canal, avec un record mondial sur le duo taux d’échantillonnage et bande passante au cur du traitement des signaux ultra-rapides.

Le composant visé n’est pas un processeur grand public, mais un circuit critique, le track-and-hold, qui attrape un signal analogique et le maintient juste assez longtemps pour qu’un convertisseur puisse le numériser proprement. Le travail a été mené en Allemagne, à l’Université de Paderborn, au Heinz Nixdorf Institute, dans le cadre du projet PACE, avec des partenaires cités comme RWTH Aachen, le Karlsruhe Institute of Technology et DESY. Sur le papier, l’intérêt est clair, plus le goulot analogique-numérique recule, plus les systèmes de communication, d’IA et de cloud peuvent absorber des flux massifs sans perdre d’information.

L’Université de Paderborn vise le goulot track-and-hold à 500 Gbps

Le record annoncé concerne un circuit track-and-hold intégré en SiGe, capable d’atteindre 500 Gbps sur un canal, avec la meilleure combinaison jamais démontrée entre taux d’échantillonnage et bande passante. Dit autrement, ce bloc élargit la fenêtre utile avant numérisation, là où beaucoup d’architectures se heurtent à des limites analogiques, même quand le reste de la chaîne numérique progresse.

Dans une chaîne de réception, ce type de circuit intervient avant l’ADC, le convertisseur analogique-numérique. Si le track-and-hold est trop lent, on peut avoir de la distorsion, du jitter, ou une capture imparfaite des variations rapides, et derrière, même un traitement numérique très sophistiqué compense mal. Marc, ingénieur télécom, résume le point de douleur, tu peux empiler des algos, si ton entrée est mal échantillonnée, tu reconstruis du bruit.

Il faut aussi garder la tête froide, 500 Gbps ne veut pas dire que demain votre smartphone télécharge à cette vitesse. On parle d’un élément de laboratoire et d’architecture, pas d’un produit final. Le passage vers des systèmes industrialisés impose des contraintes d’intégration, de packaging, de validation et de rendement. Mais pousser ce maillon précis, c’est souvent ce qui débloque, ensuite, des générations entières de liaisons et d’instrumentation.

Le projet PACE cible IA, cloud et réseaux à très haut débit

Les chercheurs lient directement cette avancée aux besoins de communication temps réel, d’intelligence artificielle et d’infrastructure cloud. L’argument est pragmatique, des modèles plus gros et des échanges plus rapides exigent des voies d’entrée-sortie qui suivent, sinon la latence monte et le débit utile chute. Un track-and-hold plus performant aide à numériser des signaux plus larges, plus vite, ce qui compte dans les interconnexions et l’instrumentation réseau.

On peut imaginer des usages concrets côté opérateurs et data centers, par exemple des modules d’optique ou des liaisons de backhaul où la qualité de capture du signal conditionne la correction d’erreur et la modulation. Quand les marges se resserrent, gagner sur la bande passante d’échantillonnage peut éviter de surdimensionner ailleurs. Marc le formule sans détour, si tu peux mesurer et convertir plus proprement, tu économises des couches de complexité.

Nuance importante, l’annonce parle d’un record sur une combinaison de métriques dans un bloc spécifique, pas d’un saut garanti sur toute la pile réseau. Entre un circuit et un système, il y a l’alimentation, la dissipation thermique, les interconnexions, la cohabitation avec d’autres blocs, et la reproductibilité en fabrication. Le potentiel est réel, mais il faudra des démonstrateurs plus proches des usages pour chiffrer l’impact sur un lien complet.

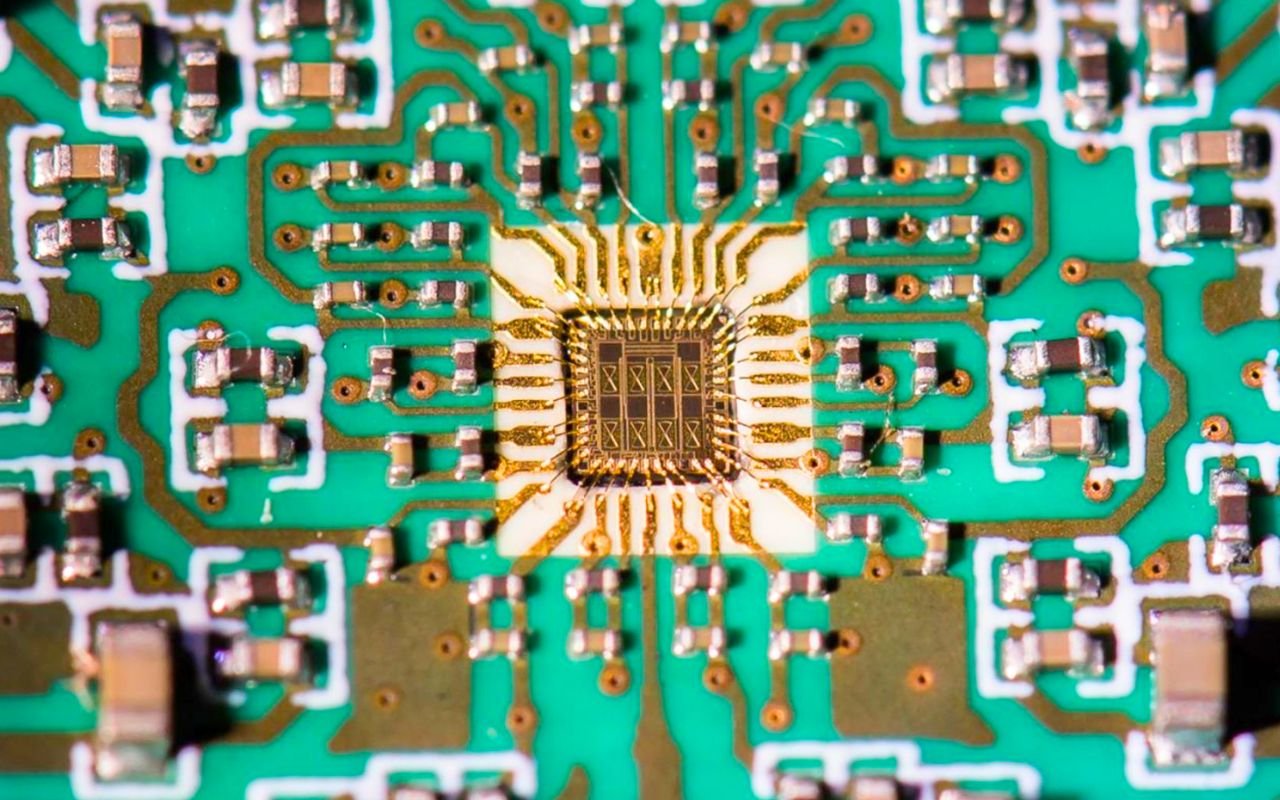

Le silicium-germanium confirme son rôle face au CMOS et au terahertz

Cette performance remet en avant le silicium-germanium comme compromis industriel, on conserve une compatibilité avec l’écosystème silicium tout en gagnant en performance électronique sur certains usages RF et très haut débit. Dans l’industrie, le SiGe HBT est souvent cité pour délivrer des fonctions RF avec moins de puissance que du CMOS à niveau comparable, ce qui explique sa présence historique dans des circuits de communication.

Le record de Paderborn s’inscrit dans une trajectoire plus longue. Dès 2014, une collaboration entre l’IHP en Allemagne et Georgia Tech avait déjà montré un transistor SiGe à 798 GHz fMAX, au prix de températures très basses, avec l’idée que des vitesses record à température ambiante n’étaient pas loin. Le message est cohérent, on pousse progressivement les limites, et chaque démonstration crédible rapproche des applications robustes.

D’autre part, un autre axe de recherche met l’accent sur le germanium sur silicium et la mobilité des porteurs, avec la promesse de composants plus rapides et plus sobres, potentiellement utiles aussi pour des dispositifs quantiques. Tout ça ne dit pas que le SiGe remplacera tout, le CMOS reste imbattable sur le coût et le volume, et chaque matériau a ses contraintes. Mais les records successifs montrent une stratégie, attaquer les goulets là où le silicium pur atteint ses plafonds.

Sources

- Silicon-germanium chip hits 500 Gbps, sets world bandwidth record

- Paderborn chip achieves 500Gb/s single-channel rate | Fibre Systems

- Silicon-Germanium Chip Sets New Speed Record | News Center

- A 1950s material just set a modern record for lightning-fast chips | ScienceDaily

- Introduction to Silicon-Germanium (SiGe) Technology – AnySilicon